### **Exposures from Mask Aligner into Resist**

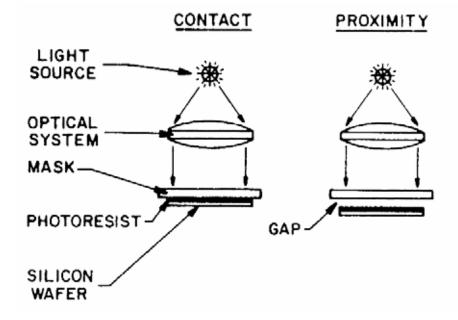

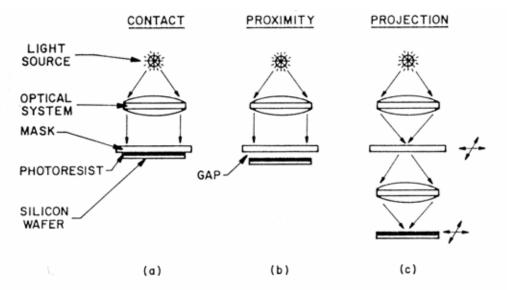

- Mask aligner images created by shadowing from mask into resist

- Soft contact and Proximity good for 3 micron structures

- Vacuum Hard Contact: no shadow effects at edge but gets mask dirty

- Size of mask structure & wavelength determines distance

- Smaller line, or shorter wavelength closer object

| Table 7.4 | Maximum allowable proximity gap for near and deep UV sources as a function of the feature size normalized |

|-----------|-----------------------------------------------------------------------------------------------------------|

|           | to the gap required for 2.5 µm resolution with a deep UV source                                           |

| Feature Size (µm) | Maximum Gap for<br>Near UV Source | Maximum Gap for<br>Deep UV Source |

|-------------------|-----------------------------------|-----------------------------------|

| 2.5               | 0.63                              | 1.0                               |

| 2.0               | 0.37                              | 0.61                              |

| 1.0               | 0.08                              | 0.24                              |

| 0.5               | 0.05                              | 0.07                              |

Data taken from Lin.

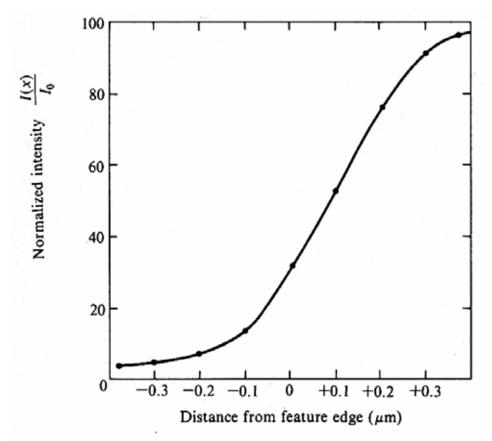

#### **Exposure Near Mask Structure Edges**

- Diffraction & shadowing cause non abrupt exposure

- Light changes gradually from zero to full Intensity

- Causes a variation in line width after development

- Hence resolution limitation ~2 micron on non contact aligner

Figure 5-14 Light intensity near the image edge. The geometrical edge of this mask feature is at x = 0. N.A. = 0.42,  $\lambda = 436$  nm, S = 0.7, linewidth = spacewidth = 0.75  $\mu$ m. (After Ref. 3. Reprinted with permission of Solid State Technology, published by Technical Publishing, a company of Dun & Bradstreet.)

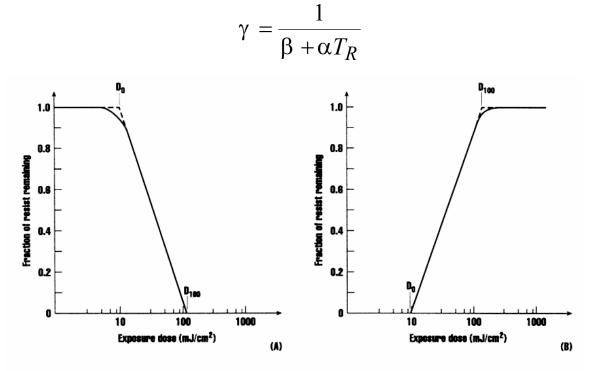

#### **Contrast Curves and Resist**

- What fraction of resist is removed for given exposure

- Define two exposure points

- $D_{100}$ : Energy (mW/cm<sup>2</sup>) where resist just affected

- $D_0$ : Energy where resist full removed after exposure

- Make a straight line projection on semilog plog

- Contrast γ is the resulting slope

$$\gamma = \frac{1}{\log_{10} \left(\frac{D_{100}}{D_0}\right)}$$

- Typical contrast  $\gamma = 2 3$

- Light absorbed by resist thickness T<sub>R</sub> is

$$A = \exp(-\alpha T_R)$$

• Thus the contrast becomes

Figure 8-7 Contrast curves for idealized resists: (a) positive tone and (b) negative tone.

### **Critical Modulation Transfer Function**

• Brightest to darkest part of exposure is Modulation Transfer Function (MTF):

$$MTF = \frac{I_{\max} - I_{\min}}{I_{\max} + I_{\min}}$$

- Measure resist with Critical Modulation Transfer Function (CMTF)

- Minimum optical modulation needed to create pattern

$$CMTF = \frac{D_{100} - D_0}{D_{100} + D_0}$$

• Using the constrast ratio

$$CMTF = \frac{10^{1/\gamma} - 1}{10^{1/\gamma} + 1}$$

- Typical CMTF about 0.4

- MTF must exceed CMTF for successful exposure

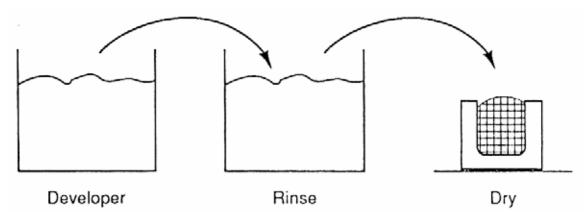

#### **Development Process**

- Developer Mixed (usually 1:1 with DI water)

- Simple method: dunk in tanks time: 30 60 sec.

- Rinse in DI after Development

- Spin Dry

Figure 9.6 Immersion developer steps.

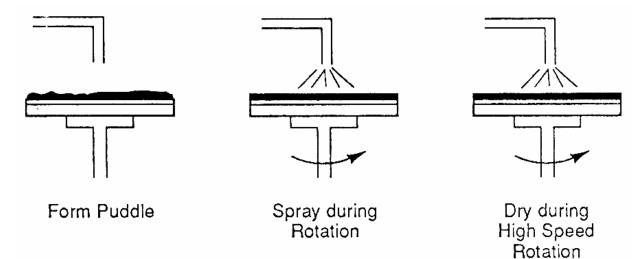

### Wafer Track Development Systems

- Automatic development similar to spin coaters

- Puddle developer,

- Spin with spray make even

- High speed rinse and spin dry

- Often do auto hard bake as well

Figure 9.8 Puddle-spray development.

### **Photoresist Exposure/Development**

- Development removal rate of resist is a function of exposure

- Unexposed resist removed (etched) at a low rate eg 0.2 nm/sec

- Exposed resist rate removal dependent on

- UV light level: higher intensity, faster removal eg. 75 mJ/cm<sup>2</sup> develops resist at 10 nm/sec eg. 150 mJ/cm<sup>2</sup> develops resist at 20 nm/sec

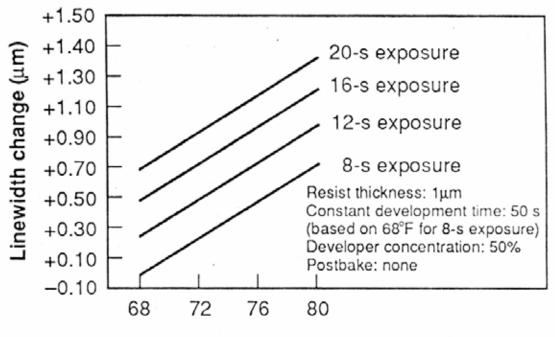

- Develop rate increases with temperature

- Rate increases with developer concentration

Developer Temperature (°F)

Figure 9.4 Developer temperature and exposure relationship versus line-width change.

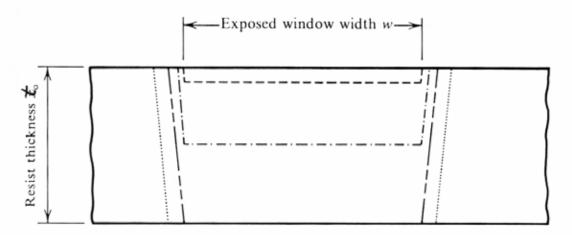

#### **Resist Hole/Line Width vs Development Time**

• Let x<sub>0</sub> be the proper development time to clear resist from the structures

$$x_0 = \frac{t_0}{d_r}$$

where  $t_0 = film$  thickness

$d_r$  = rate of resist development removal

- If  $< x_0$  get remnant resist

- If  $> x_0$  get bloated holes, narrow lines

- Always get some resist loss at top (side etching and ramp of exposure edge

Resist profile at (time  $\times$  develop rate) =

$$----- 0.1x_{o} \\ ----- 0.5x_{o} \\ ------ 1.0x_{o} \\ 2.0x_{o}$$

Figure 4-10 The evolution of positive resist development with time. Note that with time the pattern widens as well as deepens.

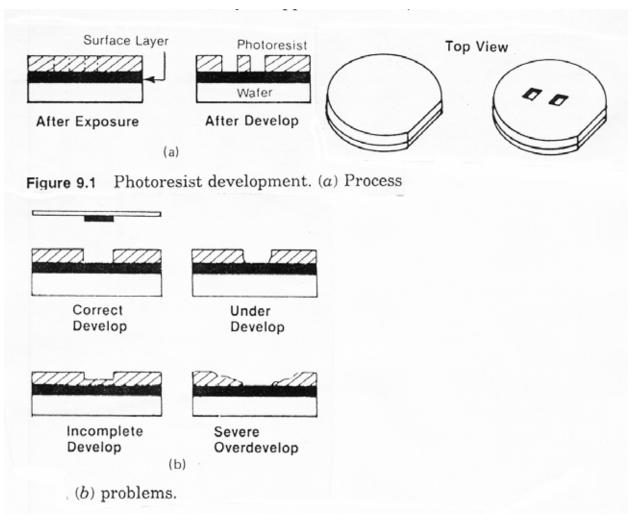

### **Proper Clearing of Resist**

- Perfect Development

- Smallest holes (vias) clear of resist at bottom

- Smallest lines acceptable width

- No "stringers" between closest lines

- Usually overdevelop 5-10% so all structures clear

- Incomplete development: thick resist in openings

- Underdeveloped: sloped edges at bottom may leave resist scum (especially small opens)

- Overdeveloped: sloped sidewalls of resist Lines too small (may disappear or lift off)

### Mask Image Transfer to Resist Pattern I Mask x Optical system ľ Image х Image-resist interaction Ζ Ideal resist pattern x Reflectivity effects Z Modified resist pattern x Substrate topography z Real resist x pattern r

### **Mask Image Transfer to Resist Pattern**

Figure 5-12 Factors affecting linewidth accuracy of resist images.

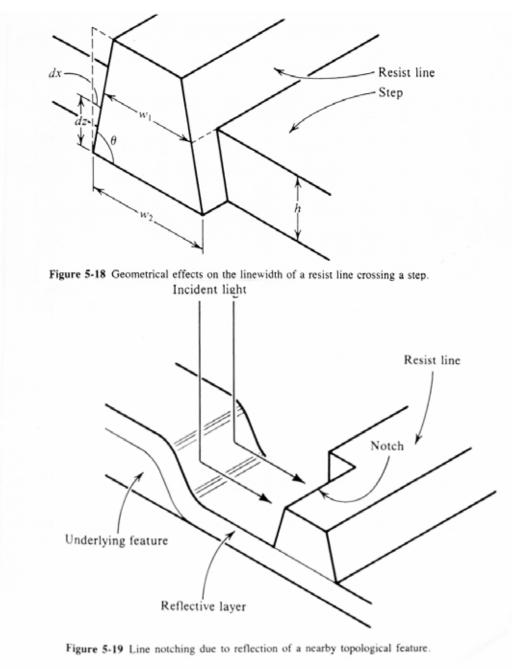

#### **UV Reflection from Wafer Surface**

- Wafer surface reflects UV back through resist

- Dull surface (oxide) small reflection & little effect

- Reflective surface (aluminum), significant effect exposure level much reduced

- At high resolution worry about optical interference in resist

- 1/4 wavelength effects create ripples in resist Standing wave patterns

- High resolution remove this: antireflection coatings multilayer resist (different index of refraction)

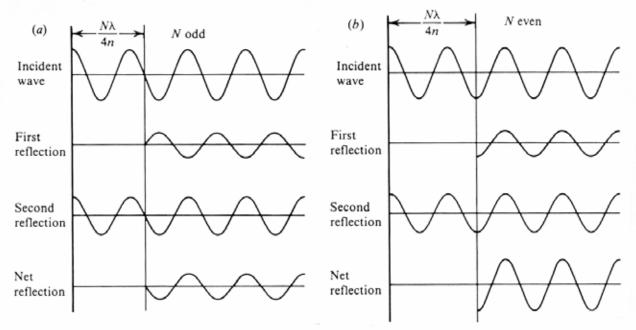

**Figure 5-16** Standing wave effects in resist. (a)  $z_0 = (N/4n)\lambda$ , N odd. Destructive interference, low reflectivity, high absorption. (b)  $z_0 = (N/4n)\lambda$ , N even. Constructive interference, high reflectivity, low absorption.

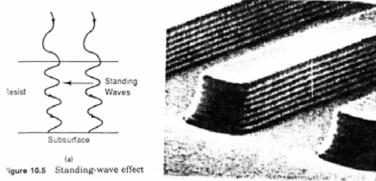

### **Topology Effects on Resist**

- Going over a step resist becomes very thick

- Hard to expose, and develop evenly

- Also wider lines due to less development

- Reflection from adjacent structures reduces nearby structure width (notch in lines)

- Need to understand fab process & adjust layout to correct

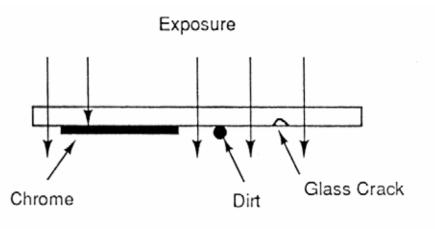

### **Mask Defects**

- Mask defects the most deadly problem

- Repeat same defect on every wafer

- Typical problems

- Dirt on mask (may come from resist) solution: clean mask (easier with Chrome mask)

- Crack in glass, or scratched mask solution: replacement mask

- Photoemulsion masks last about 100 wafers

- Chrome almost indefinite: but more expensive

- Typical Mask cost \$500-\$1000

(a)

(ь)

Figure 8.19 (a) Clear-field mask with dirt particle and glass crack, (b) result in negative resist after develop.

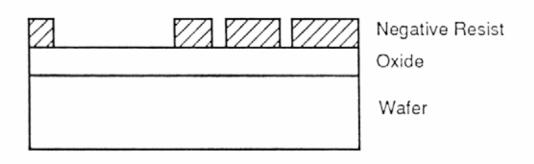

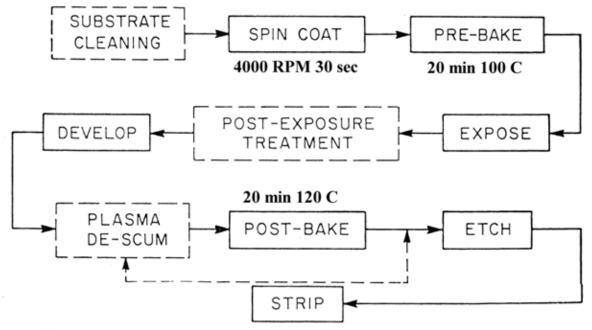

### **Photolith Hard Bake and Etching**

- Sometimes do Plasma desum remove small remnant resist

- Hard Bake makes resist tougher against etching drives off more solvent

- Typically 120°C for 20 minutes Note soft bake was at 100 °C

- If hard too short/or low temp does not resist etch

- If hard too long/or high temp trouble striping resist

- Etching next

- Strip resist only with etch is desired level

Fig. 14 Flow chart of a typical resist process. Steps in broken lines are not used for materials. Reprinted from Ref. 8 with permission of the American Chemical Society.

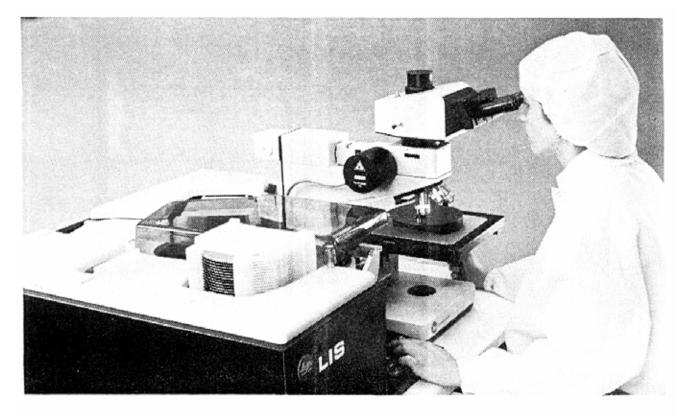

### Wafer Inspection

- Always do test exposure at a level

- Calibrate light source/resist/developer for day

- Look for over/under development

- Centre of wafer: tends to underdevelopment

- Outer wafer: tends to overdevelopment

- Inspection done in yellow light often before hard bake

- Watch for resist defects: Pin holes, fish eyes, gel slugs, hard spots (after strip)

- Auto inspection stations

- Move to specified sites on wafer: check most difficult point

- Eg Leitz LIS, cost about \$150,000 + film thickness measurement

- used for photolith and after etching

Photograph of a wafer inspection station.

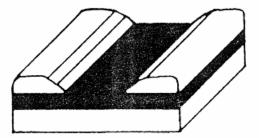

### **High Temperature Resist Flow**

- At high Temperatures > 200 °C resist flows

- Creates sloped sidewalls

- Occurs in some processes (eg Ion Implantation)

- Heated resist Hard to strip

Normal temperature

High temperature

Figure 9.9 Resist flow at high temperature.

## **Photoresist Stripping**

- Stripping extremely important for next process

- Major worry: remnant resist

## **Major Processes**

- Solvent Strippers: Acetone

- Phenol-based organic strippers

- Inorganic strippers (Nitric/Sulfuric acids)

- Plasma Strippers

- Watch for "stringers" at step edges

- edge bead thick resist very difficult to remove may make special long exposure of edge only to remove

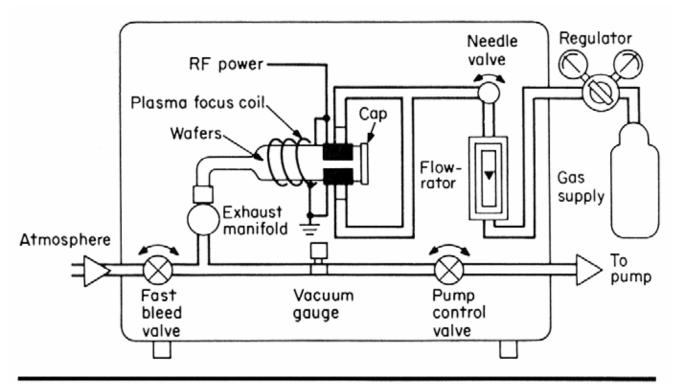

Figure 12.3 Plasma system diagrammatic cross section. (Courtesy of LFE Corp.)

### **Types of Exposure Systems**

- Mask aligner earliest & lowest cost

- Vacuum Hard Contact: no shadow effects at edge but gets mask dirty

- Soft contact and Proximity good for >2 microns

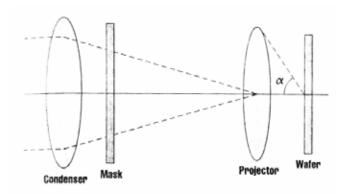

- Projection systems: Optically project image using lens system

- Expensive but low mask damage

- Use 1:1 or 5:1 reduction (whole wafers)

- 5:1 or 10:1 reduction for step and repeat

Fig. 11 Schematic of three optical lithographic techniques. (a) Contact. (b) Proximity. (c) Projection<sup>27</sup>. Copyright 1983, Bell Telephone Laboratories, Incorporated.

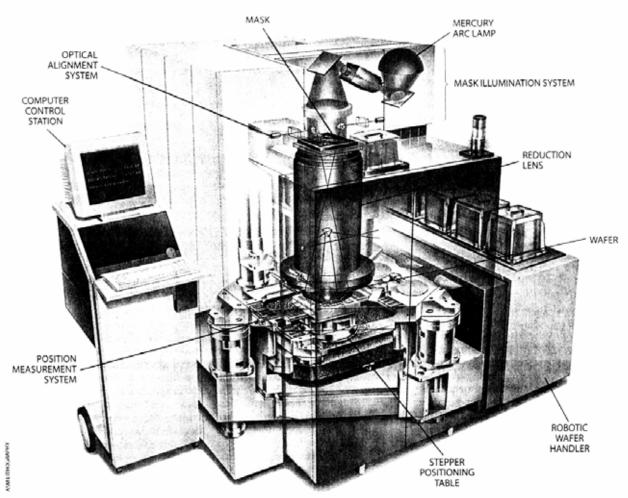

#### **Wafer Steppers**

- Called Direct Step on Wafer (DSW) or Steppers

- All systems < 2 microns

- Project one reticule print at a time

- Step to next chip site and repeat over wafer

- Reticules up to 3x3 cm now: may be one or several chips

- Table position uses laser interferometry for < 0.1 micron

- Lens most expensive point

STEPPER, or photolithography machine, imprints circuit patterns on silicon wafers. Ultraviolet light from an arc lamp (or from a laser) passes through a mask bearing the image of the

circuit. A sophisticated lens apparatus reduces the image and projects it onto part of a wafer. The table then moves, or "steps," to expose other chips.

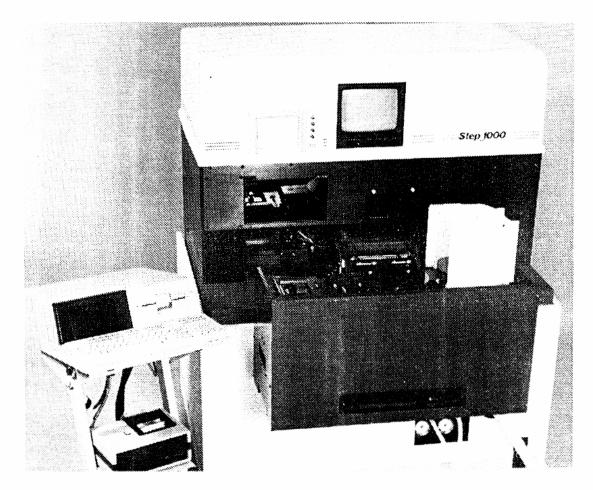

## **Direct Step on Wafer (DSW)**

- Typical cost \$0.5-\$1.5 million

- Cost depends on resolution and reticule area

- Moving to laser light sources (single wavelength) for less expensive lenses

IX Stepper: courtesy of Ultratech Stepper

#### **Projection Steppers Limits**

- Lenses best every made: diffraction limited

- Important factor in lens is Numerical Aperature

$NA = n \sin(\alpha)$

- Typical NA 0.16 0.5 for steppers

- Smallest object projected set by

$$W_{\min} = k_1 \frac{\lambda}{NA}$$

- $k_1$  depends on resist and other factors ~0.7

- Depth of focus

$$\sigma = k_2 \frac{\lambda}{NA^2}$$

- k<sub>2</sub> also dependent on exposure system

- Thus sorter wavelength means more care with focus

Figure 7-17 Schematic for the optical train of a simple projection printer.

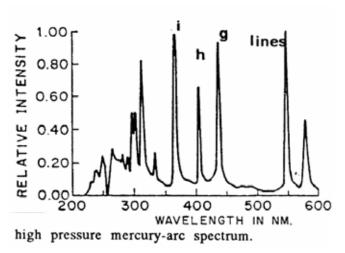

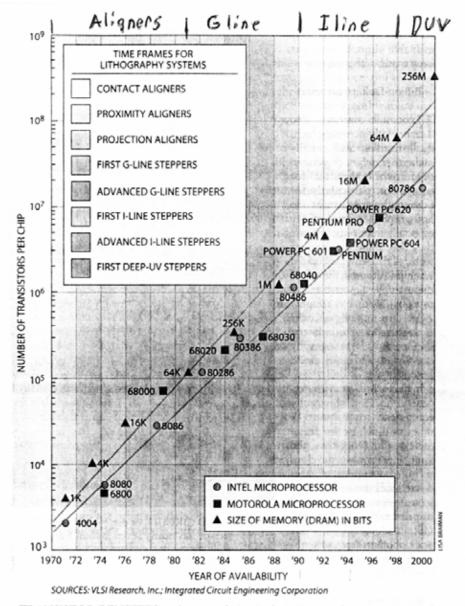

#### Wavelength and Steppers

- First Steppers use Mercury Vapour lamp souce

- Filters allow single line from source

- 1980: G line (439 nm ) steppers > 0.8 microns

- 1990: I line (365 nm) steppers > 0.3 microns (widely used)

- Now Eximer laser sources (KrF 248 nm, ArF 193 nm)

- Problem: lens material limits at short wavelength

- Can produce 0.08 micron devices with these

TRANSISTOR DENSITIES on integrated circuits have increased at an exponential rate, as shown on this logarithmic plot. The rate has been sustained by a succession of lithography systems, which are used in chipmaking to project patterns onto wafers. Higher densities have been achieved in memory chips because of their more regular and straightforward design.

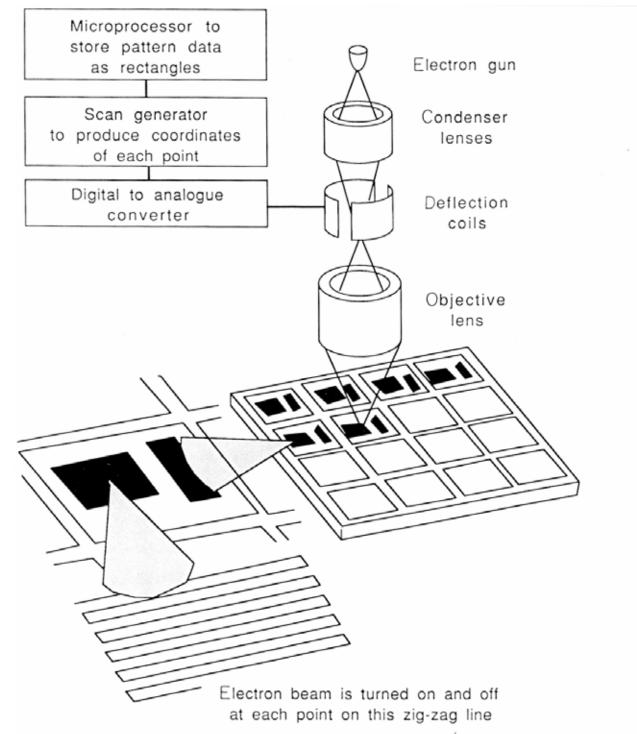

## E Beam Direct Write Systems

- E beams already used in mask creation

- Slow: beam raster scans each area on wafer

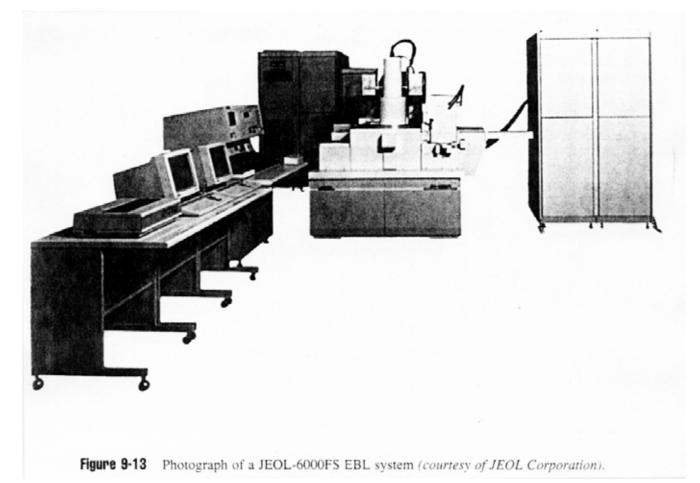

Fig. 5.8 Illustrating an electron beam lithography facility. Note the resemblance to a conventional scanning electron microscope (SEM)

### E beam Direct Write

- E beam still quite slow: raster scan

- By comparison optical prints whole mask at one

- Used mostly for Mask production & experimental devices

### X-ray Lithography

- Very high resolution > 0.3 microns

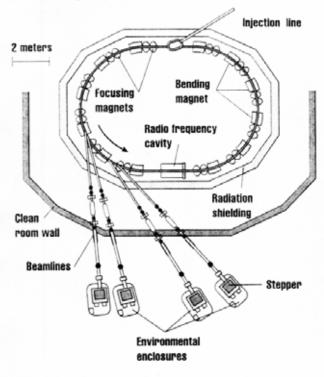

- First ones needed Synchrotron source price \$1 billion

- IBM most pushing this

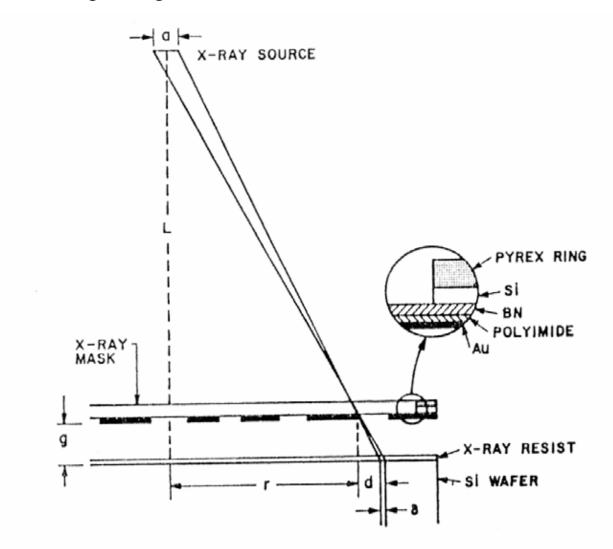

Geometric effects in x-ray lithography. Insert shows x-ray mask<sup>33</sup>

### X-ray Lithography

- Uses 1:1 thus problem creating the mask

- Difficult with resist: use plastic: PMMA

- Experimental only

- has been about to replace optical since 1980!

Electron storage ring source

Figure 9-16 Basic schematic of an electron storage ring for XRL. Several exposure stations are indicated (after Glendenning and Cerrina, reprinted by permission, Noyes Publications).

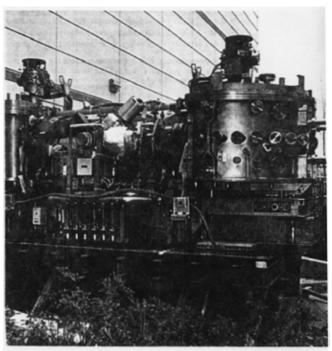

SYNCHROTRON, the only one of its kind in the U.S. designed for commercial mar ufacturing, is unloaded into IBM's East Fishkill, N.Y., facility on March 29, 1991.

### **Comparison of Lithography Systems**

- Putting in order of cost effectiveness

- Contact Mask aligner still lowest cost but resolution limited > 3 microns (80 Wafer/hr)

- 1:1, 5:1 Projections limited to > 1.5 microns

- 10:1 DSW now production standard to 0.25 microns (50 wafers/hr typical)

- Deep UV (ArF 193 nm & F<sub>2</sub> 157 nm Eximer) working in lab

- Death of Optical Lithography often predicted but optical keep pushing limits

- 157 nm Interference Phase shift masking pushing 0.08 microns! below problem limit of transistor size at 0.1 micron

LITHOGRAPHY DEVELOPMENT in the U.S. calls for increasingly smaller wavelengths of light and other forms of electromagnetic energy to produce chips with ever larger memory capacity. The procession of chip generations will require moving to ever smaller wavelengths of ultraviolet light and then perhaps to x-rays or electron beams.

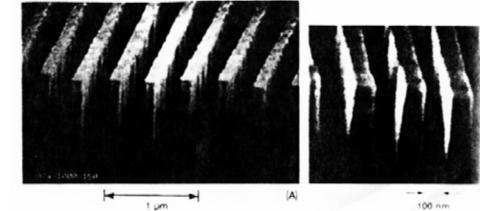

Figure 8-16: (a) 0.2 μm and (b) 0.15 μm lines imaged in 30 nm poly(nbutylsilyne)

## Next Generation Lithography Project (NGL)

- Semitech (organization of main fab companies) Project for Next Generation Lithography (ie 2005 AD)

- Aims at device geometery below 35 nm (0.035 micron)

- 4 main contenters

- Extreme UV Optical EUV (13.4 nm)

- X-ray

- Scalpel (multiple e-beam systems by Lucent)

- Ion Projection Lithography Uses ion beams to project an image

- Current (2000) projection is EUV most popular

- Semitech Projections as of 2003 were:

- 180 nm (current) 248 nm ArF Excimer DSW's

- 130 nm (~2001) 193 nm KrF Excimer DSW's

- 90 nm approx limit of 193 nm KrF's

- 70 nm 157 F<sub>2</sub> Excimer DSW's

- 50-35 nm EUV

### **Immersion Lithography: A New Breakthrough**

- Semitech 2003 assumed 157nm F<sub>2</sub> Excimer DSW's as next step

- Problem is 157 nm has lots of problems

- Lens materials no longer SiO<sub>2</sub> but instead CaF

- Very delicate, soft materials, optically seldom used

- Suffers Birefingence: index of refraction differs with direction

- F<sub>2</sub> Excimer difficult to use

- Old idea suddenly revived: Immersion Lithography

- Immerse lens & wafer in a high index fluid (DI water)

- Effective reduces wavelength of light by n (index of refraction)

$$\lambda_n = \frac{\lambda}{n}$$

- Use modified 193 nm steppers: same KrF Examer & lens

- Now get 133 nm effective source ( $n_{water} = 1.44$ )

- Effectively increases Numerical Aperature

$$NA = n \sin(\alpha)$$

- NA goes from 0.5- 0.7 to 0.7 and targets > 1

- Since smallest object projected set by

$$W_{\min} = k_1 \frac{\lambda}{NA}$$

- Significantly increases resolution possibly to 40 nm range

- Cost is reduced Depth of focus is reduced

$$\sigma = k_2 \frac{\lambda}{NA^2}$$

• Decision by Semitech mid 2004

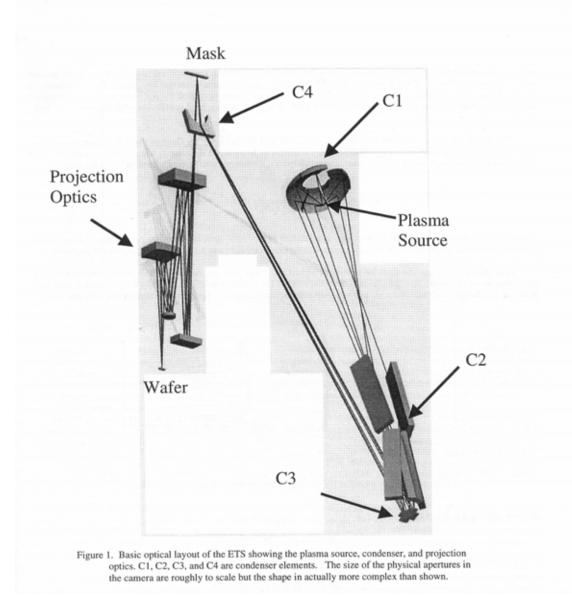

### **Extreme UV Lithography (EUV)**

- Under development at Lawrence Livermore Lab & Sandia

- Uses Laser Produced Plasma Source (LPS)

- Uses Nd:Yag laser focused on copper wire

- Creates a plasma with 13.4 nm EUV emission

- Near X-ray but acts like light (not too pentrating)

- Must use grazing mirror reflectors for 10X stepper

- Probably will exceed the ultimate transistor limits.

Sweeney, SPIE 3331, pg 2 (1998)

## **Resists for Next Generation Lithography**

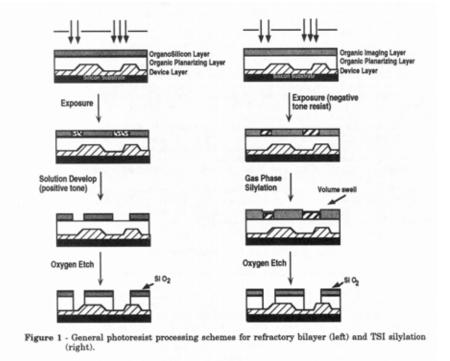

- Use Thin Layer Imaging (TLI) process

- At 157 & 13 nm light only penetrates very thin layer

- Use an organic planerization layer (organic resist)

## **Refractory Bilayer Resist**

- Thin Organio-Silicon Layer absorbs EUV

- Development removes exposed area

- Resist left behind contains silicon

- In O plasma converst to a SiO<sub>2</sub> glass

- O plasma transfers glass pattern to resist layer

# **TSI Silyatation**

- Top organic imaging layer exposed

- Resist polymer cross links, preventing diffusion

- Silylation: aminosilane gas diffuses Si into unexposed

- O plasma converts to glass during patterning of lower resist

Henerson, SPIE 3331, pg 32 1998